電腦監(jiān)控軟件硬件設計的關鍵要素與實現(xiàn)策略

電腦監(jiān)控軟件不僅依賴復雜的軟件算法,其有效運行與精準監(jiān)控也離不開背后支撐的硬件系統(tǒng)。硬件設計作為監(jiān)控系統(tǒng)的基礎,決定了軟件的穩(wěn)定性、數(shù)據(jù)采集的精度以及整體性能的上限。本文將從核心組件、設計原則、技術實現(xiàn)與未來趨勢四個方面,深入探討電腦監(jiān)控軟件硬件設計的關鍵要素。

一、核心硬件組件構成

一套完整的電腦監(jiān)控硬件系統(tǒng)通常由以下幾個核心部分組成:

- 傳感器模塊:這是數(shù)據(jù)采集的“感官”,包括溫度傳感器(如CPU/GPU/主板溫度探頭)、電壓電流傳感器(監(jiān)測電源供應狀態(tài))、風扇轉速傳感器、以及可能的物理入侵檢測傳感器(如機箱開合檢測)。

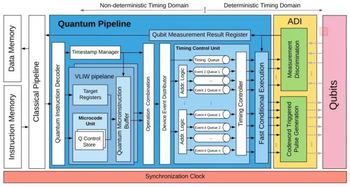

- 微控制器/專用芯片:作為硬件系統(tǒng)的“大腦”,負責接收傳感器信號,進行初步的數(shù)據(jù)處理(如模數(shù)轉換),并通過標準接口(如I2C、SMBus、USB)與主機通信。常見于主板上的Super I/O芯片或嵌入式控制器(EC)便承擔此角色。

- 信號調(diào)理與接口電路:傳感器輸出的原始信號往往微弱或帶有噪聲,需要經(jīng)過放大、濾波等調(diào)理電路,才能被微控制器準確讀取。接口電路則確保與主機連接的穩(wěn)定與兼容。

- 電源管理模塊:為所有監(jiān)控硬件提供穩(wěn)定、隔離的電源,防止因主系統(tǒng)電源波動導致監(jiān)控失效或傳感器損壞。

二、硬件設計的基本原則

- 高精度與低干擾:傳感器選型與電路設計必須確保數(shù)據(jù)采集的準確性,同時通過合理的布局布線、屏蔽和接地技術,最小化來自電腦內(nèi)部高頻數(shù)字電路的電磁干擾。

- 低功耗與高可靠性:監(jiān)控硬件常需7x24小時運行,設計應追求低功耗以降低發(fā)熱和能耗。元器件需選用工業(yè)級或商用級高可靠性產(chǎn)品,確保在復雜電磁環(huán)境和溫度變化下長期穩(wěn)定工作。

- 標準化與兼容性:硬件接口(如SMBus之于系統(tǒng)健康監(jiān)測)應遵循行業(yè)標準,確保與不同品牌、型號的主板及操作系統(tǒng)兼容。固件更新機制也應納入設計考慮。

- 安全性與非侵入性:硬件設計不應影響主系統(tǒng)的正常運行,安裝方式(如探針接觸、插接)需安全可靠。對于涉及安全監(jiān)控的硬件,還應考慮物理防篡改設計。

三、關鍵技術實現(xiàn)策略

- 分布式采集與集中管理:在復雜系統(tǒng)(如服務器集群)中,可采用分布式傳感器節(jié)點通過網(wǎng)絡(如IPMI基板管理控制器BMC)匯總數(shù)據(jù),實現(xiàn)集中監(jiān)控,降低對主機資源的占用。

- 智能預警硬件設計:除了被動采集,硬件可集成簡單的閾值比較電路,一旦參數(shù)(如溫度)超標,能直接觸發(fā)硬件級報警(如鳴響蜂鳴器、點亮LED),實現(xiàn)不依賴操作系統(tǒng)的快速響應。

- 功耗與性能平衡:在嵌入式微控制器選型時,需在計算能力、內(nèi)存、功耗和成本間取得平衡。對于簡單監(jiān)控,8位或16位MCU已足夠;對于需復雜預處理或邊緣計算的場景,則可能需要32位ARM核心。

- 模塊化設計:將傳感器模塊、處理模塊、接口模塊進行解耦設計,便于后期維護、升級和根據(jù)監(jiān)控需求靈活配置。

四、未來發(fā)展趨勢

- 集成化與智能化:未來監(jiān)控硬件將更深度地集成于主板芯片組或CPU內(nèi)部(如Intel的PECI接口),直接提供更核心的參數(shù)。具備邊緣AI計算能力的硬件能實現(xiàn)本地化的異常模式識別與預測性維護。

- 無線化與物聯(lián)網(wǎng)融合:無線傳感器網(wǎng)絡(WSN)技術使得監(jiān)控硬件部署更靈活,便于對分散的電腦設備進行統(tǒng)一監(jiān)控,并融入更廣泛的物聯(lián)網(wǎng)管理平臺。

- 安全硬件增強:隨著硬件級安全威脅增加(如側信道攻擊),監(jiān)控硬件本身的安全性將得到加強,可能集成可信平臺模塊(TPM)功能,對監(jiān)控數(shù)據(jù)的完整性和來源進行加密驗證。

電腦監(jiān)控軟件的硬件設計是一個融合了電子工程、計算機體系結構與系統(tǒng)可靠性的綜合性領域。優(yōu)秀的設計需要在精準感知、穩(wěn)定可靠、高效兼容與前瞻擴展之間找到最佳平衡點,從而為上層軟件提供堅實、可信的數(shù)據(jù)基石,共同構建起全方位、智能化的計算機系統(tǒng)健康守護網(wǎng)。

如若轉載,請注明出處:http://www.90vv.cn/product/78.html

更新時間:2026-04-22 23:36:45